# ISO<sup>2</sup>-CMOS MT9196 Integrated Digital Phone Circuit (IDPC)

Data Sheet

January 2006

#### Features

- Programmable m-Law/A-Law CODEC and Filters

- Programmable CCITT (G.711)/sign-magnitude coding

- Programmable transmit, receive and side-tone gains

- Digital DTMF and single tone generation

- Fully differential interface to handset transducers

- Auxiliary analog interface

- Interface to ST-BUS/SSI (compatible with GCI)

- Serial microport control

- Single 5 volt supply, low power operation

- Anti-howl circuit for group listening speakerphone applications

## Applications

- Digital telephone sets

- Wireless telephones

- Local area communications stations

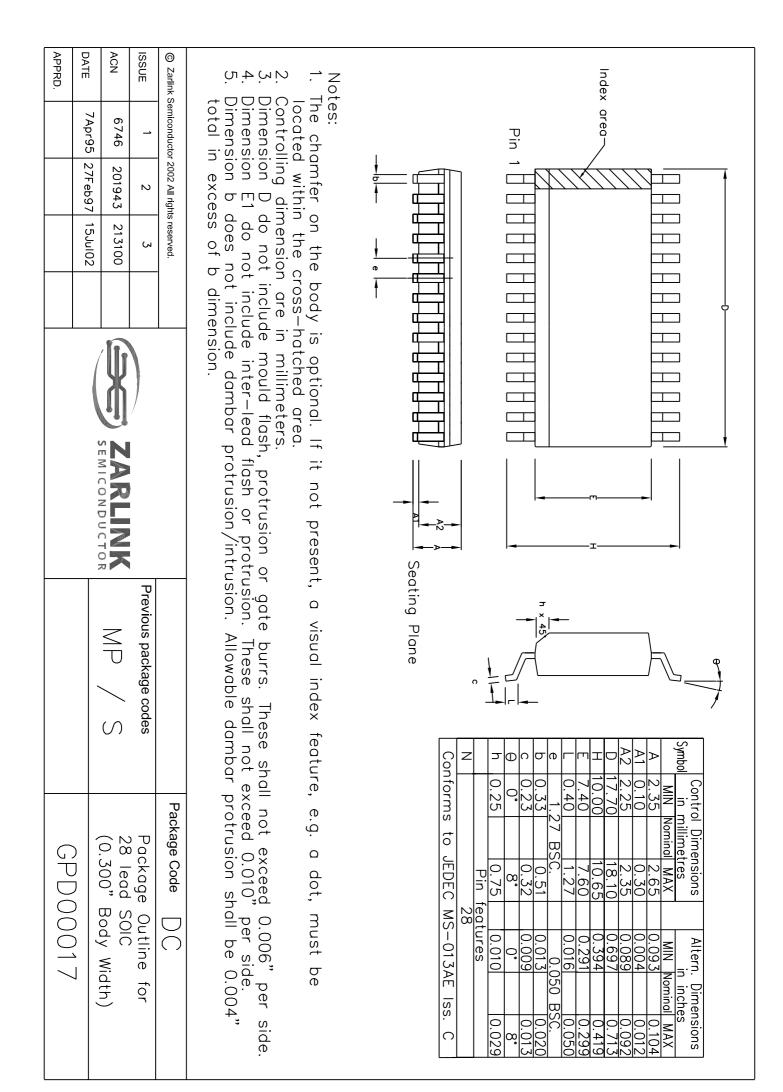

| Ordering Information                                                                                                         |                                                                                                                                                                         |                                                                                                                |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MT9196AP<br>MT9196AE<br>MT9196AS<br>MT9196ASR<br>MT9196APR<br>MT9196AE1<br>MT9196APR1<br>MT9196AS1<br>MT9196AS1<br>MT9196AS1 | 28 Pin PLCC<br>28 Pin PDIP<br>28 Pin SOIC<br>28 Pin SOIC<br>28 Pin PLCC<br>28 Pin PLCC*<br>28 Pin PLCC*<br>28 Pin PLCC*<br>28 Pin SOIC*<br>28 Pin SOIC*<br>28 Pin SOIC* | Tubes<br>Tubes<br>Tape & Reel<br>Tape & Reel<br>Tubes<br>Tape & Reel<br>Tubes<br>Tubes<br>Tubes<br>Tape & Reel |  |  |  |  |  |

|                                                                                                                              | -40°C to +85°C                                                                                                                                                          |                                                                                                                |  |  |  |  |  |

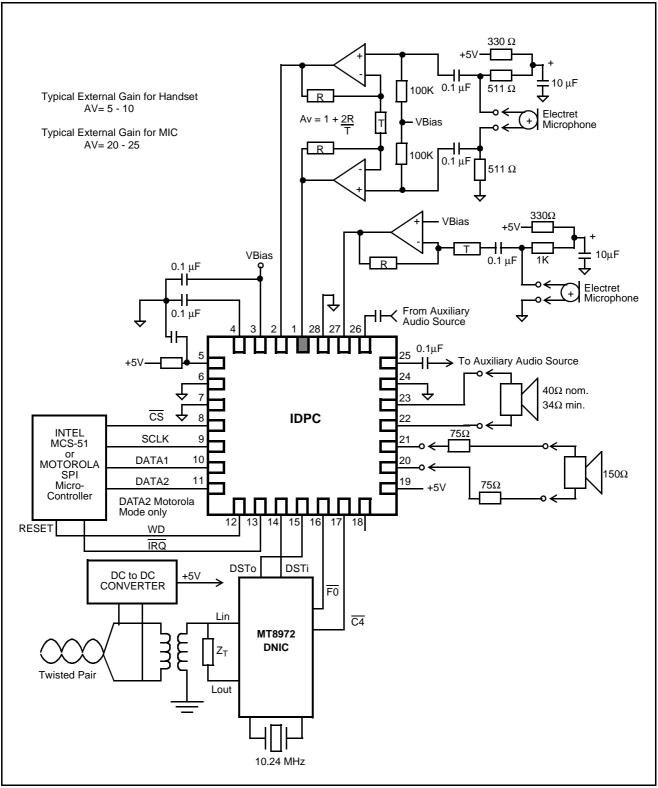

#### Description

The MT9196 Integrated Digital Phone Circuit (IDPC) is designed for use in digital phone products. The device incorporates a built-in Filter/Codec, digital gain pads, DTMF generator and tone ringer. Complete telephony interfaces are provided for connecting to handset and speakerphone transducers. Internal register access is provided through a serial microport compatible with various industry standard micro-controllers.

The device is fabricated in Zarlink's ISO<sup>2</sup>-CMOS technology ensuring low power consumption and high reliability.

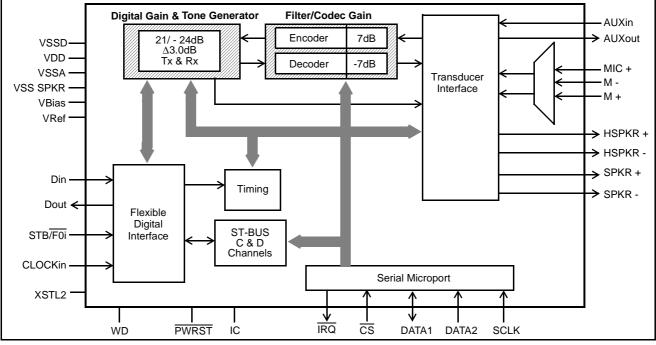

#### Figure 1 - Functional Block Diagram

1

#### VRef VBias M+ M-VSSA MIC+ AUXin 28 VSSA 27 MIC+ 26 AUXin 25 AUXout 24 VSS SPKR 23 SPKR-21 HSPKR-21 HSPKR-20 HSPKR-19 VDD 18 XSTAL2 17 CLOCKin 16 STB/F0i 15 Din 2 1 28 27 26 25 C 1 2 M-M+ 3 4 5 3 4 5 PWRST VBias AUXout VSS SPKR VRef IC **6** 24 PWRST IC VS<u>SD</u> CS SPKR+ 7 23 6 7 IC 6 VS<u>SD</u>7 CS 8 SCLK 9 DATA1 10 DATA2 11 WD 12 IRQ 13 Dout 14 ⊐ 8 22 SPKR-SCLK 21 HSPKR+ 9 20 HSPKR-DATA1 ⊐10 19 □ 13 14 15 16 17 18 □ □ □ □ □ □ □ □ 11 12 || DATA2 VDD CLOCKin XSTAL2 Din STB/F0i WD IRQ Dout 28 PIN PLCC 28 PIN SOIC/PDIP

#### Figure 2 - Pin Connections

#### **Pin Description**

| Pin # | Name              | Description                                                                                                                                                                                                                                              |  |  |  |

|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1     | M-                | <b>Inverting Microphone (Input).</b> Inverting input to microphone amplifier from the handset microphone.                                                                                                                                                |  |  |  |

| 2     | M+                | <b>Non-Inverting Microphone (Input).</b> Non-inverting input to microphone amplifier from the handset microphone.                                                                                                                                        |  |  |  |

| 3     | V <sub>Bias</sub> | <b>Bias Voltage (Output).</b> ( $V_{DD}$ /2) volts is available at this pin for biasing external amplifiers.<br>Connect 0.1 $\mu$ F capacitor to $V_{SSA}$ .                                                                                             |  |  |  |

| 4     | $V_{Ref}$         | Reference voltage for codec (Output). Nominally [ $(V_{DD}/2)$ -1.5] volts. Used internally. Connect 0.1 $\mu$ F capacitor to $V_{SSA}$ .                                                                                                                |  |  |  |

| 5     | PWRST             | Power-up Reset (Input). CMOS compatible input with Schmitt Trigger (active low).                                                                                                                                                                         |  |  |  |

| 6     | IC                | Internal Connection. Tie externally to V <sub>SS</sub> for normal operation.                                                                                                                                                                             |  |  |  |

| 7     | V <sub>SSD</sub>  | Digital Ground. Nominally 0 volts.                                                                                                                                                                                                                       |  |  |  |

| 8     | CS                | Chip Select (Input). This input signal is used to select the device for microport data transfers. Active low. TTL level compatible.                                                                                                                      |  |  |  |

| 9     | SCLK              | Serial Port Synchronous Clock (Input). Data clock for microport. TTL level compatible.                                                                                                                                                                   |  |  |  |

| 10    | DATA1             | <b>Bidirectional Serial Data.</b> Port for microprocessor serial data transfer. In Motorola/National mode of operation, this pin becomes the data transmit pin only and data receive is performed on the DATA2 pin. TTL level compatible input levels.   |  |  |  |

| 11    | DATA2             | <b>Serial Data Receive.</b> In Motorola/National mode of operation, this pin is used for data receive to the IDPC. In Intel mode, serial data transmit and receive are performed on the DATA1 pin and DATA2 is disconnected. Input level TTL compatible. |  |  |  |

| 12    | WD                | Watchdog (Output). Watchdog timer output. Active high.                                                                                                                                                                                                   |  |  |  |

| 13    | IRQ               | Interrupt Request (Open Drain Output). Low true interrupt output to microcontroller.                                                                                                                                                                     |  |  |  |

Data Sheet

#### **Pin Description (continued)**

| Pin # | Name                 | Description                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 14    | D <sub>out</sub>     | <b>Data Output.</b> A tri-state digital output for 8 bit wide channel data being sent to the Layer 1 device. Data is shifted out via this pin concurrent with the rising edge of BCL during the timeslot defined by STB, or according to standard ST-BUS timing.                                 |  |  |  |  |

| 15    | D <sub>in</sub>      | <b>Data Input.</b> A digital input for 8 bit wide channel data received from the Layer 1 device. Data is sampled on the falling edge of BCL during the timeslot defined by STB, or according to standard ST-BUS timing. Input level is CMOS compatible.                                          |  |  |  |  |

| 16    | STB/F0i              | <b>Data Strobe/Frame Pulse (Input).</b> For SSI mode this input determines the 8 bit timeslot used by the device for both transmit and receive data. This active high signal has a repetition rate of 8 kHz. Standard frame pulse definitions apply in ST-BUS mode. CMOS level compatible input. |  |  |  |  |

| 17    | CLOCKin              | <b>Clock Input.</b> The clock provided to this input is used by the internal phone functions. In ST-BUS mode this is the C4i input. In SSI synchronous mode, this is the Bit Clock input. In SSI-asynchronous mode this is an asynchronous 4 MHz Master Clock input.                             |  |  |  |  |

| 18    | XSTL2                | Crystal Input (4.096 MHz). Used in conjunction with the CLOCKin pin to provide the master clock signal via external crystal.                                                                                                                                                                     |  |  |  |  |

| 19    | V <sub>DD</sub>      | Positive Power Supply (Input). Nominally 5 volts.                                                                                                                                                                                                                                                |  |  |  |  |

| 20    | HSPKR-               | Inverting Handset Speaker (Output). Output to the handset speaker (balanced).                                                                                                                                                                                                                    |  |  |  |  |

| 21    | HSPKR+               | Non-Inverting Handset Speaker (Output). Output to the handset speaker (balanced).                                                                                                                                                                                                                |  |  |  |  |

| 22    | SPKR-                | Inverting Speaker (Output). Output to the speakerphone speaker (balanced).                                                                                                                                                                                                                       |  |  |  |  |

| 23    | SPKR+                | Non-Inverting Speaker (Output). Output to the speakerphone speaker (balanced).                                                                                                                                                                                                                   |  |  |  |  |

| 24    | V <sub>SS</sub> SPKR | Power Supply Rail for Speaker Driver. Nominally 0 Volts.                                                                                                                                                                                                                                         |  |  |  |  |

| 25    | AUX <sub>out</sub>   | Auxiliary Port (Output). Access point to the D/A (analog) signals of the receive path as well as to the various analog inputs.                                                                                                                                                                   |  |  |  |  |

| 26    | AUX <sub>in</sub>    | Auxiliary Port (Input). An analog signal may be fed to the filter/codec transmit section and various loopback paths via this pin. No external anti-aliasing is required.                                                                                                                         |  |  |  |  |

| 27    | MIC+                 | Non-inverting on-hook answer back Microphone (Input). Microphone amplifier non-<br>inverting input pin.                                                                                                                                                                                          |  |  |  |  |

| 28    | V <sub>SSA</sub>     | Analog Ground (Input). Nominally 0 V.                                                                                                                                                                                                                                                            |  |  |  |  |

## Overview

The functional block diagram of Figure 1 depicts the main operations performed by the MT9196 IDPC. Each of these functional blocks will be described individually in the sections to follow. This overview will describe some of the end-user features which may be implemented as a direct result of the level of integration found within the IDPC.

The main feature required of a digital telephone is to convert the digital Pulse Code Modulated (PCM) information, being received by the telephone set, into an analog electrical signal. This signal is then applied to an appropriate audio transducer such that the information is finally converted into intelligible acoustic energy. The same is true of the reverse direction where acoustic energy is converted first into an electrical analog and then digitized (into PCM) before being transmitted from the set. Along the way if the signals can be manipulated, either in the analog or the digital domains, other features such as gain control and signal generation may be added. Finally, most electro-acoustic transducers (loudspeakers) require a large amount of power if they are to develop an acoustic signal. The inclusion of audio amplifiers to provide this power is required.

The IDPC features complete Analog/Digital and Digital/Analog conversion of audio signals (Filter/CODEC) and an analog interface to electro-acoustic devices (Transducer Interface). Full programmability of the receive path and side-tone gains is available to set comfortable listening levels for the user. Transmit path gain control is available for setting nominal transmit levels into the network. A digital, anti-feedback circuit permits both the handset microphone and the speaker-phone speaker to be enabled at the same time for group listening applications. This anti-feedback circuit limits the total loop gain there by preventing a singing condition from developing.

Signalling in digital telephone systems, behind the PBX or standard ISDN applications, is handled on the D-channel and generally does not require DTMF tones. Locally generated tones, in the set, however, can be used to provided "comfort tones" or "key confirmation" to the user, similar to the familiar DTMF tones generated by conventional phones during initial call set-up. Also, as the network slowly evolves from the dial pulse/DTMF methods to the D-Channel protocols it is essential that the older methods be available for backward compatibility. As an example, once a call has been established (i.e., from your office to your home) using the D-Channel signalling protocol it may be necessary to use in-band DTMF signalling to manipulate your personal answering machine in order to retrieve messages. Thus the locally generated tones must be of network quality. The IDPC can generate the required tone pairs as well as single tones to accommodate any in-band signalling requirement.

Each of the programmable parameters within the functional blocks is accessed through a serial microcontroller port compatible with Intel MCS-51<sup>®</sup>, Motorola SPI<sup>®</sup> and National Semiconductor Microwire<sup>®</sup> specifications.

## Functional Description

In this section each of the functional blocks within IDPC is described along with all of the associated control/status bits. Each time a control/status bit(s) is described it is followed by the address register where it will be found. The reader is referred to the section titled 'Register Summary' for a complete listing of all address registers, the control/status bits associated with each register and a definition of the function of each control/status bit. The Register Summary is useful for future reference of control/status bits without the need to locate them in the text of the functional descriptions.

#### Filter/CODEC

The Filter/CODEC block implements conversion of the analog 3.3 kHz speech signals to/from the digital domain compatible with 64 kb/s PCM B-Channels. Selection of companding curves and digital code assignment are register programmable. These are CCITT G.711 A-law or  $\mu$ -Law, with true-sign/ Alternate Digit Inversion or true-sign/Inverted Magnitude coding, respectively. Optionally, sign- magnitude coding may also be selected for proprietary applications.

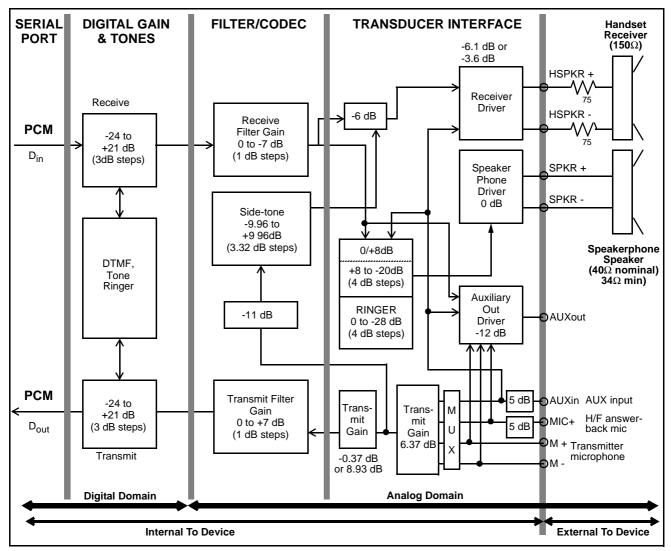

The Filter/CODEC block also implements transmit and receive audio path gains in the analog domain. These gains are in addition to the digital gain pad section and provide an overall path gain resolution of 1.0 dB. A programmable gain, voice side-tone path is also included to provide proportional transmit speech feedback to the handset receiver. Figure 3 depicts the nominal half-channel and side-tone gains for the IDPC.

On  $\overline{PWRST}$  (pin 5) the Filter/CODEC defaults such that the side-tone path, dial tone filter and 400 Hz transmit filter are off, all programmable gains are set to 0 dB and CCITT  $\mu$ -Law is selected. Further, the Filter/CODEC is powered down due to the control bits of the Path Control Registers (addresses 12h and 13h) being reset.

The internal architecture is fully differential to provide the best possible noise rejection as well as to allow a wide dynamic range from a single 5 volt supply design. This fully differential architecture is continued into the Transducer Interface section to provide full chip realization of these capabilities for the handset and loudspeaker functions.

A reference voltage (V<sub>Ref</sub>), for the conversion requirements of the CODEC section, and a bias voltage (V<sub>Bias</sub>), for biasing the internal analog sections, are both generated on-chip. V<sub>Bias</sub> is also brought to an external pin so that it may be used for biasing external gain plan setting amplifiers. A 0.1  $\mu$ F capacitor must be connected from V<sub>Bias</sub> to analog ground at all times. Likewise, although V<sub>Ref</sub> may only be used internally, a 0.1  $\mu$ F capacitor from the V<sub>Ref</sub> pin to ground is required at all times. The analog ground reference point for these two capacitors must be physically the same point. To facilitate this the V<sub>Ref</sub> and V<sub>Bias</sub> pins are situated on adjacent pins.

The transmit filter is designed to meet CCITT G.714 specifications. The nominal gain for this filter path is 0 dB (gain control = 0 dB). Gain control allows the output signal to be increased up to 7 dB. An anti-aliasing filter is included. This is a second order lowpass implementation with a corner frequency at 25 kHz. Attenuation is better than 32 dB at 256 kHz and less than 0.01 dB within the passband.

An optional 400 Hz high-pass function may be included into the transmit path by enabling the Tfhp bit in the Control Register 1 (address 0Eh). This option allows the reduction of transmitted background noise such as motor and fan noise.

#### Figure 3 - Audio Gain Partitioning

The receive filter is designed to meet CCITT G.714 specifications. The nominal gain for this filter path is 0 dB (gain control = 0dB). Gain control allows the output signal to be attenuated up to 7 dB. Filter response is peaked to compensate for the sinx/x attenuation caused by the 8 kHz sampling rate.

The Rx filter function can be altered by enabling the Dial EN control bit in Control Register 1 (address 0Eh). This causes another low-pass function to be added with a 3 dB point at 1200 Hz. This function is intended to improve the sound quality of digitally generated dial tone received as PCM.

Side-tone is derived from the Tx filter before the LP/HP filter section and is not subject to the gain control of the Tx filter section. Side-tone is summed into the receive handset transducer driver path after the Rx filter gain control

section so that Rx gain adjustment will not affect side-tone levels. The side-tone path may be enabled/disabled with the Voice sidetone bit located in the Receive Path Control Register (address 13h).

Transmit and receive filter gains are controlled by the  $TxFG_0$ - $TxFG_2$  and  $RxFG_0$ - $RxFG_2$  control bits, respectively. These are located in the FCODEC Control Register 1 (address 0Ah). Transmit filter gain is adjustable from 0 dB to +7 dB and receive filter gain from 0 dB to -7 dB, both in 1 dB increments.

Side-tone filter gain is controlled by the  $STG_0$ - $STG_2$  control bits located in the FCODEC Control Register 2 (address 0Bh). Side-tone gain is adjustable from -9.96 dB to +9.96 dB in 3.32 dB increments.

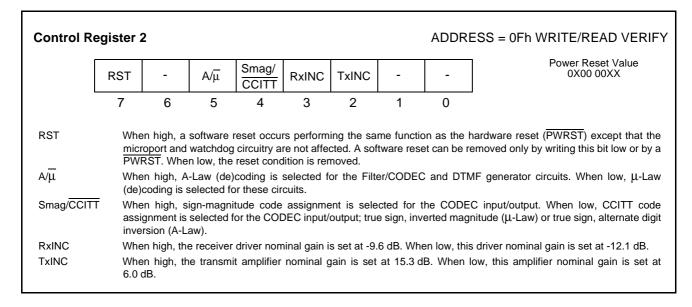

Companding law selection for the Filter/CODEC is provided by the A/ $\mu$  companding control bit while the coding scheme is controlled by the sign-mag/CCITT control bit. Both of these reside in Control Register 2 (address 0Fh). Table 1 illustrates these choices.

| Code                  | Sign/     | CCITT (G.711) |           |  |  |

|-----------------------|-----------|---------------|-----------|--|--|

| Code                  | Magnitude | μ <b>-Law</b> | A-Law     |  |  |

| + Full Scale          | 1111 1111 | 1000 0000     | 1010 1010 |  |  |

| + Zero                | 1000 0000 | 1111 1111     | 1101 0101 |  |  |

| -Zero<br>(quiet code) | 0000 0000 | 0111 1111     | 0101 0101 |  |  |

| - Full Scale          | 0111 1111 | 0000 0000     | 0010 1010 |  |  |

Table 1

The Filter/CODEC autonull circuit ensures that transmit PCM will contain no more than  $\pm 1$  bit of offset due to internal circuitry.

#### Digital Gain and Tone Generation

The Digital gain and Tone generator block is located, functionally, between the serial FDI port and the Filter/CODEC block. Its main function is to provide digital gain control of the transmit and receive audio signals and to generate digital patterns for DTMF and tone ringer signals.

#### Gain Control

Gain control is performed on linear code for both the receive and the transmit PCM. Gain control is set via the Digital Gain Control Register at address 19h. Gain, in 3.0 dB increments, is available within a range of +21.0 dB to -24 dB.

#### **DTMF Generator**

The digital DTMF circuit generates a dual sine-wave pattern which may be routed into the receive path as comfort tones or into the transmit path as network signalling. In both cases the digitally generated signal will undergo gain adjustment as programmed into the transmit and receive gain control registers. Gain control is assigned automatically as functions are selected via the transmit and receive path control registers.

The composite signal output level in the transmit direction is -4 dBm0 ( $\mu$ -Law) and -10 dBm0 (A-law) with programmable gains at zero dB. Pre-twist of 2.0 dB is incorporated into the composite signal resulting in a low tone output level of -8.12 dBm0 and a high group level of -6.12 dBm0 (for  $\mu$ -Law, 6 dB lower for A-Law). Note that these levels will be influenced by the Anti-Howling circuit when it is enabled (see Anti-Howling section for more details). DTMF side-tone levels are set to -28 dBm0 from the generator circuit. Other receive path gains must be included when calculating the analog output signal levels. Adjustments to these levels may be made by altering the settings of the Gain Control register (address 19h).

The frequency of the low group tone is programmed by writing an 8-bit coefficient into the Low Tone Coefficient Register (address 1Ah) while the high group tone frequency uses the 8-bit coefficient programmed into the High Tone Coefficient Register (address 1Bh). Both coefficients are determined by the following equation:

Frequency (in Hz) = 7.8125 x COEFF

Where COEFF is an integer between 0 and 255. Frequency resolution is 7.8125 Hz in the range 0 to 1992 Hz.

Low and high tones are enabled individually via the LoEn and HiEN control bits (DTMF/Ringer Control Register, address 18h). This not only provides control over dual tone generation but also allows single tone generation using either of the enable bits and its associated coefficient register.

After programming and enabling the tone generators as described, selection of transmit and/or receive path destinations are carried out via the Path Control Registers (see Path Control section). In addition receive sidetone DTMF must be selected via the DTMF StEN bit (DTMF/Tone ringer Register, address 18h) so that it replaces the received PCM in the Rx Filter path.

| Frequency<br>(Hz) | COEFF | Actual<br>Frequency | %<br>Deviation |

|-------------------|-------|---------------------|----------------|

| 697               | 59h   | 695.3               | 20%            |

| 770               | 63h   | 773.4               | +.40%          |

| 852               | 6Dh   | 851.6               | 05%            |

| 941               | 79h   | 945.3               | +.46%          |

| 1209              | 9Bh   | 1210.9              | +.20%          |

| 1336              | ABh   | 1335.9              | .00%           |

| 1477              | BDh   | 1476.6              | 03%            |

| 1633              | D1h   | 1632.8              | 01%            |

#### Table 2 - DTMF Frequencies

DTMF Signal to distortion:

The sum of harmonic and noise power in the frequency band from 50 Hz to 3500 Hz is typically more than 30 dB below the power in the tone pair. All individual harmonics are typically more than 40 dB below the level of the low group tone.

Table 2 gives the standard DTMF frequencies, the coefficient required to generate the closest frequency, the actual frequency generated and the percent deviation of the generated tone from the nominal.

#### Tone Ringer

A dual frequency squarewave ringing signal may be applied to the handsfree speaker driver to generate a call alerting signal. To enable this mode the Ring En bit (address 18h) must be set as well as the ringer function to the loudspeaker via the Receive Path Control Register (address 13h). Ring En is independent of the DTMF enable control bits (see Lo EN and Hi EN). Since both functions use the same coefficient registers they are not usually enabled simultaneously.

The digital tone generator uses the values programmed into the low and high Tone Coefficient Registers (addresses 1Ah and 1Bh) to generate two different squarewave frequencies.

Both coefficients are determined by the following equation:

COEFF = [32000/Frequency (Hz)] - 1

where COEFF is an integer between 1 and 255. This produces frequencies between 125 - 16000 Hz with a non-linear resolution.

The ringer program switches between these two frequencies at a 5 Hz or 10 Hz rate as selected by the WR bit in the DTMF/Tone ringer register (address 18h).

#### Anti-Howl

IDPC includes an Anti-Howling circuit plus speaker gain control circuit to allow for group listening operation. Although this is the main function of the circuit there are additional modes in which it may be used as defined by the MS1 and MS0 control bits (address 1Ch).

| 0 | 0 | Tx noise reduction (squelch)  |

|---|---|-------------------------------|

| 0 | 1 | Rx noise reduction (squelch)  |

| 1 | 0 | switched loss group listening |

|   |   | (anti-howling)                |

| 1 | 1 | Tx/Rx switched loss           |

The circuit is enabled by setting the Anti-howl Enable bit (address 1Ch) and selecting the required operational mode (MS0 & MS1) as described.

For all modes of operation the switching levels and inserted loss are programmed as follows.

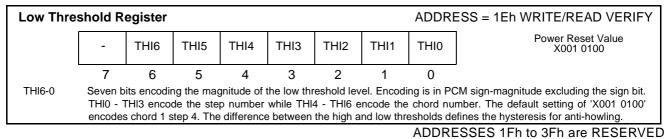

Switching decisions are made by comparing either the transmit or the receive signal level to threshold levels stored in the High Threshold Register (address 1Dh) and the Low Threshold Register (address 1Eh). Threshold data is encoded in PCM sign-magnitude format excluding the sign bit. For example; THh0 - THh3 encode the PCM step number while THh4 - THh6 encode the PCM chord number for the high threshold. Similarly for the THI0 - THI6 bits of the low threshold. The difference between the high and low threshold levels provides the circuit with hysteresis to prevent uncontrolled operation. The low level threshold must never be programmed to a value higher than the one stored in the high level threshold. If this occurs the circuit will become unstable.

Loss is implemented, in the chosen path, by subtracting the value set by the Pad0 - Pad3 control bits from the appropriate gain value set by the RxG0 - RxG3 or TxG0 - TxG3 control bits (see Digital Gain Register, address 19h). The minimum digital gain is limited to -24 dB regardless of the mathematical result of this operation. The path without loss reverts to the gain value programmed into the Digital Gain Register.

The magnitude of the switched loss defaults to 12 dB on power up but can be programmed to between 0 and 21 dB using the Pad0 - Pad2 control bits (address 1Ch).

| Pad2 | Pad1 | Pad0 | Attenuation (dB) |

|------|------|------|------------------|

| 0    | 0    | 0    | 0                |

| 0    | 0    | 1    | 3                |

| 0    | 1    | 0    | 6                |

| 0    | 1    | 1    | 9                |

| 1    | 0    | 0    | 12               |

| 1    | 0    | 1    | 15               |

| 1    | 1    | 0    | 18               |

| 1    | 1    | 1    | 21               |

#### Switched Loss for Group Listening (anti-howling)

Group listening is defined as a normal handset conversation with received speech also directed to the loudspeaker for third party observation. In this mode, if the handset microphone is moved into close proximity of the loudspeaker a feedback path will occur resulting in a singing connection. To prevent this the anti-howling circuit introduces a switched loss into either the transmit or receive paths dependent upon the transmit path speech activity.

Loss switching is determined by comparing the signal level in the transmit path with the high level threshold stored at address 1Dh. When the transmit signal level exceeds this threshold the programmed loss is switched from the transmit path to the receive path. Once switching has occurred the transmit signal level is then compared to a low level threshold stored at address 1Eh. When the transmit signal level falls below this threshold the programmed loss is switched from the transmit signal level falls below this threshold the programmed loss is switched from the received path back to the transmit path and comparison reverts back to the high threshold level.

Since the received digital gain control is used to set the listening level of the received speech, for both handset receiver and loudspeaker, it is necessary to provide additional gain in the loudspeaker path so that its receive level can be controlled independently from the receiver output. The Gain0 to Gain3 control bits (address 0Bh) are used to boost the loudspeaker output to a comfortable listening level for the third parties in group listening. Generally the Gain3 bit should be set to logic 1 in this mode. This increases the gain programmed via the Gain0 - Gain2 bits by a factor of 8 dB. In group listening a speaker gain setting of 4 to 16 dB will be required to set a comfortable group listening level after the handset user has adjusted their listening level as required.

Since the anti-howling circuit has dynamic control over the transmit and receive gain control registers, it is recommended that this function be turned off momentarily when DTMF tone generation is required. This will ensure that the proper transmit levels are attained.

#### Transmit Noise Reduction (squelch)

The transmit signal may be muted to eliminate transmission of excessive background noise.

In this mode the signal level in the transmit path is compared with the high level threshold stored at address 1Dh. When the transmit signal level exceeds this threshold no loss is inserted into the transmit path. After exceeding the high level threshold the transmit signal level is then compared to a low level threshold stored at address 1Eh. When the transmit signal level falls below this threshold the transmit digital gain is reduced by the programmed amount (Pad0-2) and comparison reverts back to the high threshold level. The receive path gain is not altered by transmit noise reduction.

#### **Receive Noise Reduction (squelch)**

The receive signal may be muted to eliminate background noise resulting from a poor trunk connection.

In this mode the signal level in the receive path is compared with the high level threshold stored at address 1Dh. When the receive signal level exceeds this threshold no loss is inserted into the receive path. After exceeding the high level threshold the receive signal level is then compared to a low level threshold stored at address 1Eh. When the receive signal level falls below this threshold the receive digital gain is reduced by the programmed amount (Pad2-0) and comparison reverts back to the high threshold level. The transmit path gain is not altered by receive noise reduction.

#### Tx/Rx Switched Loss

In this mode the programmed switched loss is inserted into either the transmit or receive path dependent only upon activity in the receive path. If receive path activity is above the programmed high level threshold then the switched loss is inserted into the transmit path. If receive path activity is below the programmed low level threshold then the switched loss is inserted into the receive path.

This mode can be used to implement a loudspeaking function where the receive audio is routed to the SPKR± pins and transmit audio is sourced from the MIC+ pin. In this mode there is no algorithmic cancellation of echo so it is recommended that this switched loss program be used only in 4-wire systems (i.e., digital set to digital set).

#### **Transducer Interfaces**

Four standard telephony transducer interfaces plus an auxiliary I/O are provided by the IDPC. These are:

- The handset microphone inputs (transmitter), pins M+/M- and the answerback microphone input MIC+. The nominal transmit path gain may be adjusted to either 6.0 dB or 15.3 dB. Control of this gain is provided by the TxINC control bit (Control register 2, address 0Fh). This gain adjustment is in addition to the programmable gain provided by the transmit filter and Digital Gain circuit.

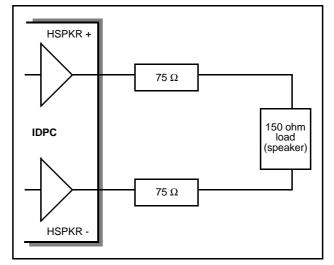

- The handset speaker outputs (receiver), pins HSPKR+/HSPKR-. This internally compensated, fully differential output driver is capable of driving the load shown in Figure 4. The nominal handset receive path gain may be adjusted to either -12.1 dB or -9.6 dB. Control of this gain is provided by the RxINC control bit (Control

register 2, address 0Fh). This gain adjustment is in addition to the programmable gain provided by the receive filter and Digital Gain circuit.

- The loudspeaker outputs, pins SPKR+/SPKR-. This internally compensated, fully differential output driver is capable of directly driving 6.5v p-p into a 40 ohm load.

- The Auxiliary Port provides an analog I/O, pins AUXin and AUXout, for connection of external equipment to the CODEC path as well as allowing access to the speaker driver circuits.

- AUXin is a single ended high impedance input (>10 Kohm). This is a self-biased input with a maximum input range of 2.5vp-p. Signals should be capacitor-coupled to this input.

- AUXout is a buffered output capable of driving 40 Kohms//150 pF. Signals for this output are derived from the receive path or from the AUXin and transmit microphones.

- Auxiliary port path gains are:

| AUXin to Dout   | 11 dB   | TxINC=0 |

|-----------------|---------|---------|

|                 | 20.3 dB | TxINC=1 |

| Din to AUXout   | -12 dB  |         |

| AUXin to AUXout | -7.0 dB |         |

| AUXin to HSPKR± | -1.1 dB | RxINC=0 |

|                 | 1.4 dB  | RxINC=1 |

| AUXin to SPKR±  | 5.0 dB  |         |

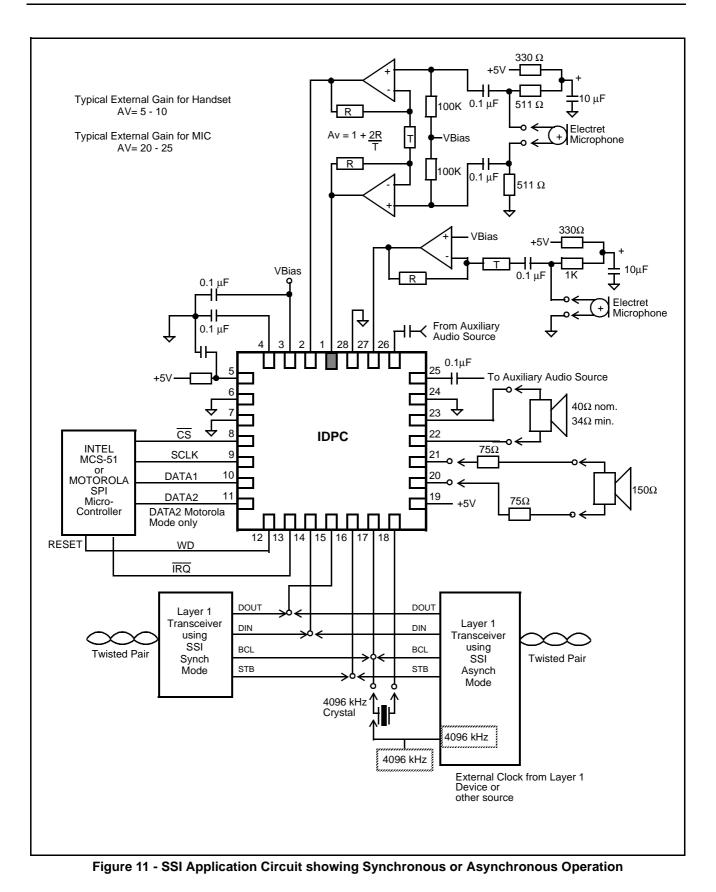

Refer to the application diagrams of Figures 10 and 11 for typical connections to this analog I/O section.

Figure 4 - Handset Speaker Driver

#### Microport

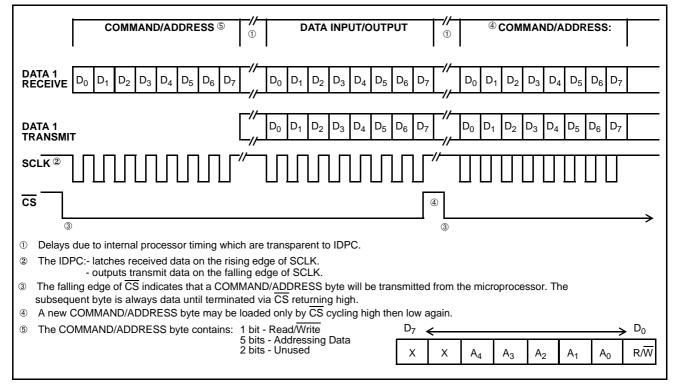

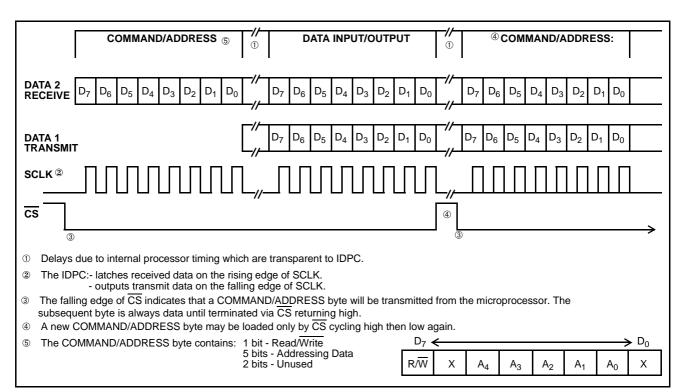

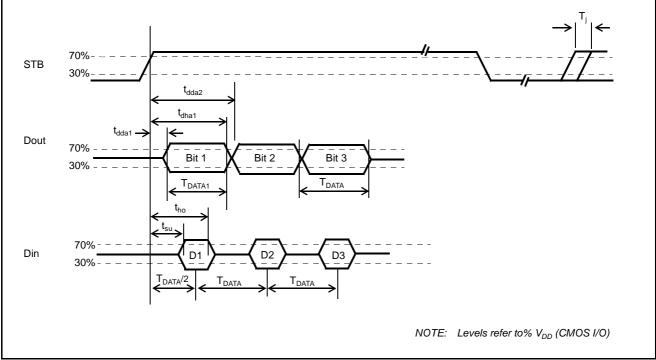

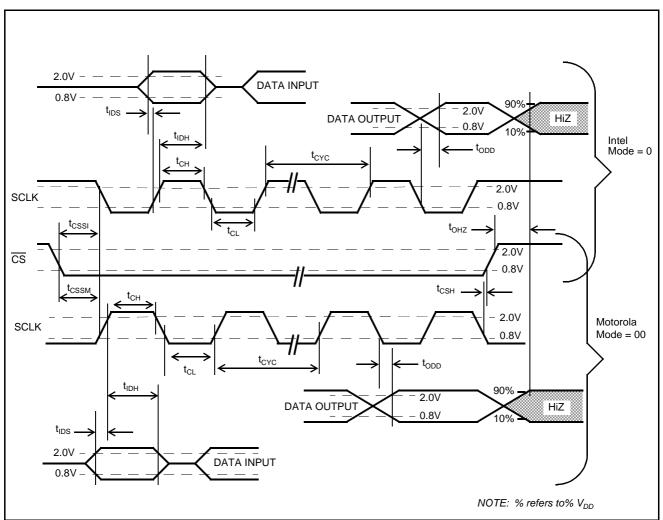

The serial microport, compatible with Intel MCS-51 (mode 0), Motorola SPI (CPOL=0,CPHA=0) and National Semiconductor Microwire specifications provides access to all IDPC internal read and write registers. This microport consists of a transmit/receive data pin (DATA1), a receive data pin (DATA2), a chip select pin (CS) and a synchronous data clock pin (SCLK).

The microport dynamically senses the state of the serial clock each time chip select becomes active. The device then automatically adjusts its internal timing and pin configuration to conform to Intel or Motorola/National requirements. If SCLK is high during chip select activation then Intel mode 0 timing is assumed. The DATA1 pin is defined as a bi-directional (transmit/receive) serial port and DATA2 is internally disconnected. If SCLK is low during chip select activation then Motorola/National timing is assumed. Motorola processor mode CPOL=0, CPHA=0 must be used. DATA1 is defined as the data transmit pin while DATA2 becomes the data receive pin. Although the dual

port Motorola controller configuration usually supports full-duplex communication, only half-duplex communication is possible in IDPC. The micro must discard non-valid data which it clocks in during a valid write transfer to IDPC. During a valid read transfer from IDPC data simultaneously clocked out by the micro is ignored by IDPC.

All data transfers through the microport are two-byte transfers requiring the transmission of a Command/Address byte followed by the data byte written or read from the addressed register.  $\overline{CS}$  must remain asserted for the duration of this two-byte transfer. As shown in Figures 5 and 6 the falling edge of  $\overline{CS}$  indicates to the IDPC that a microport transfer is about to begin. The first 8 clock cycles of SCLK after the falling edge of  $\overline{CS}$  are always used to receive the Command/Address byte from the microcontroller. The Command/Address byte contains information detailing whether the second byte transfer will be a read or a write operation and at what address. The next 8 clock cycles are used to transfer the data byte between the IDPC and the microcontroller. At the end of the two-byte transfer  $\overline{CS}$  is brought high again to terminate the session. The rising edge of  $\overline{CS}$  will tri-state the output driver of DATA1 which will remain tri-stated as long as  $\overline{CS}$  is high.

Intel processors utilize least significant bit first transmission while Motorola/National processors employ most significant bit first transmission. The IDPC microport automatically accommodates these two schemes for normal data bytes. However, to ensure timely decoding of the R/W and address information, the Command/Address byte is defined differently for Intel operation than it is for Motorola/National operation. Refer to the relative timing diagrams of Figures 5 and 6.

Receive data is sampled on the rising edge of SCLK while transmit data is made available concurrent with the falling edge of SCLK.

Detailed microport timing is shown in Figure 15.

Figure 5 - Serial Port Relative Timing for Intel Mode 0

Data Sheet

Figure 6 - Serial Port Relative Timing for Motorola Mode 00/National Microwire

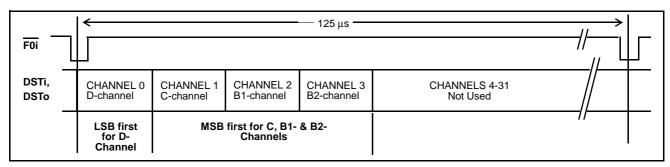

Figure 7 - ST-BUS Channel Assignment

#### Flexible Digital Interface

A serial link is required to transport data between the IDPC and an external digital transmission device. IDPC utilizes the ST-BUS architecture defined by Zarlink Semiconductor but also supports a strobed data interface found on many standard CODEC devices. This interface is commonly referred to as Synchronous Serial Interface (SSI). The combination of ST-BUS and SSI provides a Flexible Digital Interface (FDI) capable of supporting all Zarlink basic rate transmission devices as well as many other 2B + D transceivers.

The required mode of operation is selected via the ST-BUS/SSI control bit (FDI Control Register, address 10h). Pin definitions alter dependent upon the operational mode selected, as described in the following subsections as well as in the Pin Description tables.

## Quiet Code

The FDI can be made to send quiet code to the decoder and receive filter path by setting the RxMUTE bit high. Likewise, the FDI will send quiet code in the transmit (DSTo) path when the TxMUTE bit is high. Both of these

control bits reside in Control Register 1 at address 0Eh. When either of these bits are low their respective paths function normally. The -Zero entry of Table 1 is used for the quiet code definition.

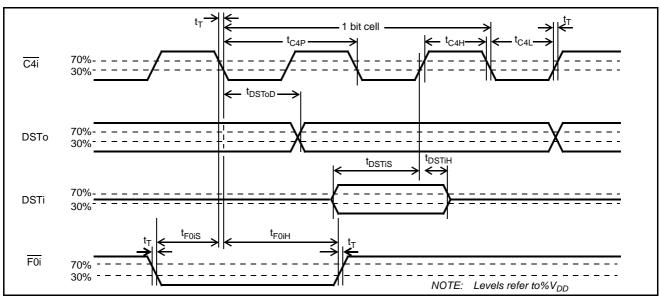

#### ST-BUS Mode

The ST-BUS consists of output (DSTo) and input (DSTi) serial data streams, in FDI these are named Dout and Din respectively, a synchronous clock input signal CLOCKin (C4i), and a framing pulse input (F0i). These signals are direct connections to the corresponding pins of Zarlink basic rate devices. Note that in ST-BUS mode the XSTL2 pin is not used. The CSL1 and CSL0 bits, as described in the SSI Mode section, are also ignored since the data rate is fixed for ST-BUS operation. However, the Asynch/Synch bit must be set to logic "0" for ST-BUS operation.

The data streams operate at 2048 kb/s and are Time Division Multiplexed into 32 identical channels of 64 kb/s bandwidth. A frame pulse (a 244 nSec low going pulse) is used to parse the continuous serial data streams into the 32 channel TDM frames. Each frame has a 125  $\mu$ Second period translating into an 8 kHz frame rate. A valid frame begins when F0i is logic low coincident with a falling edge of C4i. Refer to Figure 12 for detailed ST-BUS timing. C4i has a frequency (4096 kHz) which is twice the data rate. This clock is used to sample the data at the 3/4 bit-cell position on DSTi and to make data available on DSTo at the start of the bit-cell. C4i is also used to clock the IDPC internal functions (i.e., Filter/CODEC, Digital gain and tone generation) and to provide the channel timing requirements.

The IDPC uses only the first four channels of the 32 channel frame. These channels are always defined, beginning with Channel 0 after the frame pulse, as shown in Figure 7 (ST-BUS channel assignments).

The first two (D & C) Channels are enabled for use by the DEN and CEN bits respectively, (FDI Control Register, address 10h). ISDN basic rate service (2B+D) defines a 16kb/s signalling (D) Channel. IDPC supports transparent access to this signalling channel. ST-BUS basic rate transmission devices, which may not employ a microport, provide access to their internal control/status registers through the ST-BUS Control (C) Channel. IDPC supports microport access to this C-Channel.

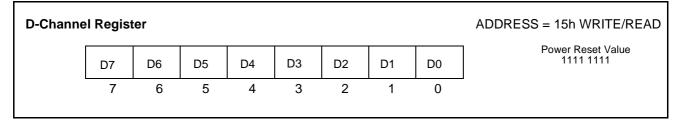

#### DEN - D-Channel

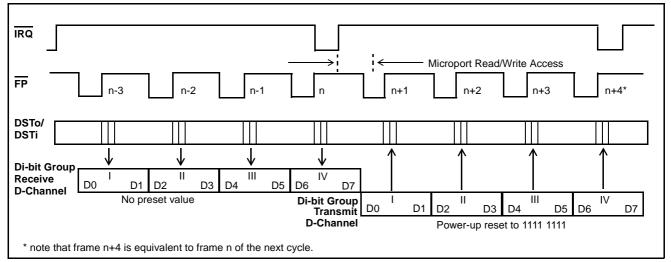

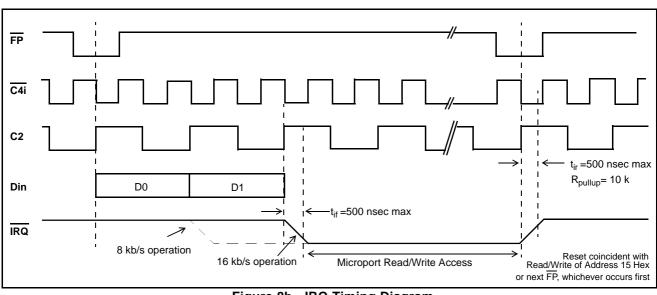

In ST-BUS mode access to the D-Channel (transmit and receive) data is provided through an 8-bit read/write register (address 15h) D-Channel data is accumulated in, or transmitted from this register at the rate of 2 bits/frame for 16 kb/s operation (1 bit/frame for 8 kb/s operation). Since the ST-BUS is asynchronous, with respect to the microport, valid access to this register is controlled through the use of an interrupt (IRQ) output. D-Channel access is enabled via the (DEn) bit.

#### <u>DEn:</u>

When 1, ST-BUS D-channel data (1 or 2 bits/frame depending on the state of the D8 bit) is shifted into/out of the D-channel (READ/WRITE) register.

When 0, the receive D-channel data (READ) is still shifted into the proper register while the DSTo D-channel timeslot and IRQ outputs are tri-stated (default).

#### <u>D8:</u>

When 1, D-Channel data is shifted at the rate of 1 bit/frame (8 kb/s).

When 0, D-Channel data is shifted at the rate of 2 bits/frame (16 kb/s default).

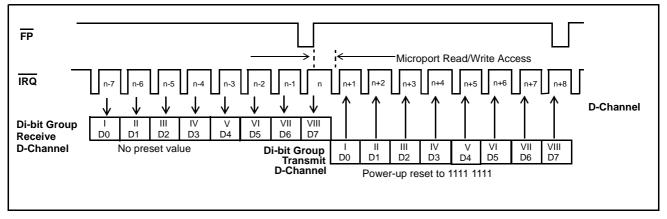

16 kb/s D-Channel operation is the default mode which allows the microprocessor access to a full byte of D-Channel information every fourth ST-BUS frame. By arbitrarily assigning ST-BUS frame n as the reference frame, during which the microprocessor D-Channel read and write operations are performed, then:

a. A microport read of address 15 hex will result in a byte of data being extracted which is composed of four di-bits (designated by roman numerals I,II,III,IV). These di-bits are composed of the two D-Channel bits received during each of frames n, n-1, n-2 and n-3. Referring to Fig. 8a: di-bit I is mapped from frame n-3, di-bit II is mapped from frame n-2, di-bit III is mapped from frame n-1 and di-bit IV is mapped from frame n.

The D-Channel read register is not preset to any particular value on power-up (PWRST) or software reset (RST).

b. A microport write to Address 15hex will result in a byte of data being loaded which is composed of four dibits (designated by roman numerals I, II, III, IV). These di-bits are destined for the two D-Channel bits transmitted during each of frames n+1, n+2, n+3, n+4. Referring to Fig.8a: di-bit I is mapped to frame n+1, di-bit II is mapped to frame n+2, di bit III is mapped to frame n+3 and di bit IV is mapped to frame n+4.

If no new data is written to address 15hex, the current D-channel register contents will be continuously retransmitted. The D-Channel write register is preset to all ones on power-up (PWRST) or software reset (RST).

An interrupt output is provided (IRQ) to synchronize microprocessor access to the D-Channel register during valid ST-BUS periods only. IRQ will occur every fourth (eighth in 8 kb/s mode) ST-BUS frame at the beginning of the third (second in 8 kb/s mode) ST-BUS bit cell period. The interrupt will be removed following a microprocessor Read or Write of Address 15 hex or upon encountering the following frames's FP input, whichever occurs first. To ensure D-Channel data integrity, microport read/write access to Address 15 hex must occur before the following frame pulse. See Figure 8b for timing.

8 kb/s operation expands the interrupt to every eight frames and processes data one-bit-per-frame. D-Channel register data is mapped according to Figure 8c.

Figure 8a - D-Channel 16 kb/s Operation

Figure 8b - IRQ Timing Diagram

Figure 8c - D-Channel 8 kb/s Operation

CEn - C-Channel

Channel 1 conveys the control/status information for the layer 1 transceiver. C-Channel data is transferred MSB first on the ST-BUS by IDPC. The full 64 kb/s bandwidth is available and is assigned according to which transceiver is being used. Consult the data sheet for the selected transceiver for its C-Channel bit definitions and order of bit transfer.

When CEN is high, data written to the C-Channel register (address 14h) is transmitted, most significant bit first, on DSTo. On power-up reset (PWRST) or software reset (RST, address 0Fh) all C-Channel bits default to logic high. Receive C-Channel data (DSTi) is always routed to the read register regardless of this control bit's logic state.

When low, data transmission is halted and this timeslot is tri-stated on DSTo.

#### B1-Channel and B2-Channel

Channels 2 and 3 are the B1 and B2 channels, respectively. B-channel PCM associated with the Digital Gain, Filter/CODEC and transducer audio paths is selected on an independent basis for the transmit and receive paths. For example, the transmit path may use the B1 channel while the receive path uses the B2 channel. Although not normally required, this flexibility is allowed.

For ST-BUS mode the configuration of bits 0 to 3, at address 12h, defines both the source of transmit audio and the B-Channel destination. The configuration of this register permits selection of only one transmit B-Channel at a time. If no valid transmit path has been selected, via the Transmit Path Selection Register, for a particular B-Channel then that timeslot output on DSTo is tri-stated.

When a valid receive path has been selected, via the Receive Path Selection Register (address 13h), the active receive B-Channel is governed by the state of the B2/B1 control bit in Control register 1 (address 0Eh).

Refer to the Path Selection section for detailed information.

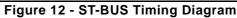

#### SSI Mode

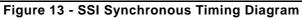

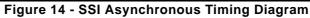

The SSI BUS consists of input and output serial data streams named Din and Dout respectively, a Clock input signal (CLOCKin), and a framing strobe input (STB). A 4.096 MHz master clock, at CLOCKin, is required for SSI operation if the bit clock is less than 512 kHz. The timing requirements for SSI are shown in Figures 13 and 14.

In SSI mode the IDPC supports only B-Channel operation. The internal C and D Channel registers used in ST-BUS mode are not functional for SSI operation. The control bit B2/B1, as described in the ST-BUS section, is ignored since the B-Channel timeslot is defined by the input STB strobe. Hence, in SSI mode transmit and receive B-Channel data are always in the channel defined by the STB input.

The data strobe input STB determines the 8-bit timeslot used by the device for both transmit and receive data. This is an active high signal with an 8 kHz repetition rate.

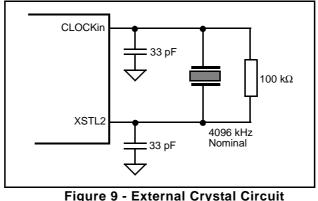

SSI operation is separated into two categories based upon the serial data rate. If the bit clock is 512 kHz or greater then the bit clock is used directly by the internal IDPC functions allowing synchronous operation. In this case, the bit clock is connected directly to the CLOCKin pin while XSTAL2 is left unconnected. If the available bit clock rate is 128 kHz or 256 kHz then a 4096 kHz master clock is required to derive clocks for the internal IDPC functions. If this clock is available externally then it may be applied directly to the CLOCKin pin. If a 4096 kHz clock is not available then provision is made to connect a 4096 kHz crystal across the CLOCKin and XSTAL2 pins as shown in Figure 9. The oscillator circuit has been designed to require an external feedback resistor and load capacitors. This configuration allows normal ST-BUS operation and synchronous SSI operation with clocks which are not loaded by these extra components.

#### igure 9 - External Crystal Circuit (for asynchronous operation)

Applications where the bit clock rate is below 512 kHz are designated as asynchronous. The IDPC will generate and re-align its internal clocks to allow operation when the external master and bit clocks are asynchronous. In this case, the external bit clock is not connected to the IDPC. Control bits Asynch/Synch, CSL1 and CSL0 in FDI Control Register (address 10h) are used to program the bit rates as shown in Table 3.

#### Data Sheet

## MT9196

| Asynch/<br>Synch | CSL1 | CSL0 | Bit Clock<br>Rate (kHz) | CLOCKin<br>(kHz)  |

|------------------|------|------|-------------------------|-------------------|

| 1                | 0    | 0    | 128                     | 4096<br>mandatory |

| 1                | 0    | 1    | 256                     | 4096<br>mandatory |

| 0                | 0    | 0    | 512                     | 512               |

| 0                | 0    | 1    | 1536                    | 1536              |

| 0                | 1    | 0    | 2048                    | 2048              |

| 0                | 1    | 1    | 4096                    | 4096              |

#### Table 3

For synchronous operation data is sampled, from Din, on the falling edge of the bit clock during the time slot defined by the STB input. Data is made available, on Dout, on the rising edge of the bit clock during the time slot defined by the STB input. Dout is tri-stated at all times when STB is not true. If STB is valid but no transmit path has been selected (via the Transmit Path Control Register) then quiet code will be transmitted on Dout during the valid strobe period. There is no frame delay through the FDI circuit for synchronous operation.

For asynchronous operation Dout and Din are as defined for synchronous operation except that data is transferred according to the internally generated bit clock. Due to resynchronization circuitry activity, the output jitter on Dout is nominally larger but will not affect operation since the bit cell period at 128 kb/s and 256 kb/s is relatively large. There is a one frame delay through the FDI circuit for asynchronous operation. Refer to the specifications of Figures 13 and 14 for both synchronous and asynchronous SSI timing.

#### Path Selection

Transmit and receive audio paths are independently programmed through their respective Path Control Registers at addresses 12h and 13h. Individual audio path circuit blocks are powered up only as they are required to satisfy the programmed values in the path control registers. More detail is provided in the Power-up/down Reset section.

#### <u>Transmit</u>

Transmit audio path configuration (Path Control Register, address 12h) is simply a matter of assigning one of the three analog signal inputs, or the digital tone generator, to the required transmit B- Channel. Intermediate functions such as the transmit filter, encoder and transmit gain are automatically powered up and assigned as required. If transmit tones is selected then the digital tone generator must be programmed and enabled properly as described in the Digital Tone Generator section. Note that transmit tones may be enabled independently of the receive path.

For ST-BUS mode the configuration of bits 0 to 3, at address 12h, defines both the source of transmit audio and the B-Channel destination. The configuration of this register permits selection of only one transmit B-Channel at a time. For SSI mode only the selections where bit 3 = 0 are allowed. This is because the B-Channel timeslot is defined by the input strobe at STB. If a selection where bit 3 = 1 is made it will be treated the same as the condition where B3 - B0 = all zero's.

All reserved configurations should not be used.

#### Receive

The receive path assignment (Receive Path Control Register, address 13h) is different from the transmit path assignment. In this case a particular analog output port is assigned a source for its audio signal. The receive filter audio path and the Auxiliary In analog port are the available choices. This configuration allows flexibility in assignment. Two examples; the receive filter path can be assigned to the handset receiver, for a standard handset conversation, while permitting the loudspeaker to announce a message originating from the Auxiliary In port. Or

perhaps the receive filter is assigned to both the loudspeaker and the Auxiliary Out port. This would allow a voice recorder or Facsimile machine, connected to the AUXout port to be monitored over the loudspeaker.

The receive filter path itself has two possible signal sources, PCM from the Din port or synthesized tones, from the digital tone generator. In both cases receive digital gain is assigned automatically. The Receive Path Control Register combines all of these choices into simple output port assignments.

In ST-BUS mode receive PCM from the Din port must be selected from either the B1 or the B2 channel. Control Bit B2/B1 in Control Register 1 (address 0Eh) is used to define the active receive B-Channel. In SSI mode the active PCM channel is automatically defined by the STB input signal.

#### **Sidetone**

A voice sidetone path provides proportional transmit signal summing into the receive handset transducer driver. Details are provided in the Filter/CODEC section.

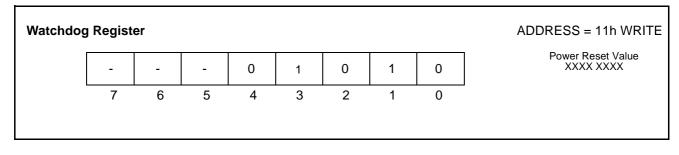

#### Watchdog

To maintain program integrity an on-chip watchdog timer is provided for connection to the microcontroller reset pin. The watchdog output WD goes high while the IDPC is held in reset via PWRST. Release of PWRST will cause WD to return low immediately and will also start the watchdog timer. The watchdog timer is clocked on the falling edge of STB/F0i and requires only this input, along with V<sub>DD</sub>, for operation. Note that in SSI mode, if STB disappears the watchdog will stop clocking. This will not harm processor operation but there is no longer any protection provided.

If the watchdog reset word is written to the watchdog register (address 11h) after PWRST is released, but before the timeout period (T=512 mSec) expires, a reset of the timer results and WD will remain low. Thereafter, if the reset word is loaded correctly at intervals less than 'T' then WD will continue low. The first break from this routine, in which the watchdog register is not written to within the correct interval or it is written to with incorrect data, will result in a high going WD output after the current interval 'T' expires. WD will then toggle at this rate until the watchdog register is again written to correctly.

#### 5-Bit Watchdog Reset Word

| B7      | <b>B6</b> | B5 | B4 | <b>B</b> 3 | B2 | B1 | <b>B0</b> |

|---------|-----------|----|----|------------|----|----|-----------|

| Х       | Х         | Х  | 0  | 1          | 0  | 1  | 0         |

| x=don't | care      |    |    |            |    |    |           |

#### Power-up/down & PWRST/Software Reset

While the IDPC is held in PWRST no device control or functionality is possible. While in software reset (RST=1, address 0Fh) only the microport and watchdog are functional. Software reset can only be removed by writing RST logic low or by the PWRST pin.

After Power-up reset ( $\overline{PWRST}$ ) or software reset (RST) all control bits assume their default states;  $\mu$ -Law functionality, usually 0 dB programmable gains and all sections of IDPC, except the microport and watchdog, into powered down states. This is the low power, stand-by condition. This includes:

- The receive output drive transducers. All transducer output drivers are powered down forcing the output signals into tri-state. Output drivers (handset, handsfree-speaker, AUXout) are powered up/down individually as required by the state of the programmed bits in the Receive Path Control Register (address 13h)

- The transmit and receive filters and CODEC. All clocks for this circuit block are disabled. The complete section is automatically powered up as required by the programmed bits in the Transmit and Receive Path Control registers (addresses 12h and 13h). Whenever all path control selections are off this section is powered down. The CODEC and transmit/ receive filters cannot be powered up individually.

- The VRef and VBias circuits. Reference and Bias voltage drivers are tri-stated during power down causing the voltage at the pins to float. This circuit block is automatically powered up/down as it is required by either the Filter/CODEC or the transducer driver circuits. Whenever all path control selections are off this section is powered down. If the AUXin path to (any combination of the) output transducer drivers is selected then the VRef/VBias circuit is powered up but the Filter/CODEC circuit is not.

- The FDI and oscillator circuits. After PWRST, the device assumes SSI operation with Dout tri-stated while

there is no strobe active on STB. If a valid strobe is supplied to STB, then Dout will be active, during the

defined channel, supplying quiet code as defined in Table 1. If the device is switched to ST-BUS operation

following PWRST, the entire Dout stream will be tri-stated until an active transmit channel is programmed. As

well, following PWRST, the oscillator circuit is disabled and all timing for the IDPC functional blocks is halted.

A clock signal applied to the MCL pin is prevented from entering further into the IDPC when the

Asynch/Synch bit is logic "1".

To power up the FDI and oscillator circuits the PD bit of Control Register 1 (address 0Eh) must be cleared.

To attain complete power-down from a normal operating condition, write all "0s" to the <u>Transmit</u> and Receive Path Control Registers (address 12h and 13h), set PD to logic 1 at address 0Eh, and Asynch/Synch to logic 1 at address 10h.

## Data Sheet

## IDPC Register Map

| 00<br>•<br>•<br>09 | RESERVED         |                         |                             |                             |                  |                   |                   |                   |                    |

|--------------------|------------------|-------------------------|-----------------------------|-----------------------------|------------------|-------------------|-------------------|-------------------|--------------------|

| 0A                 | -                | $RxFG_2$                | $RxFG_1$                    | $RxFG_0$                    | -                | TxFG <sub>2</sub> | TxFG <sub>1</sub> | TxFG <sub>0</sub> | FCodec Control 1   |

| 0B                 | Gain3            | Gain2                   | Gain1                       | Gain0                       | -                | STG <sub>2</sub>  | $STG_1$           | STG <sub>0</sub>  | FCodec Control 2   |

| 0C                 |                  |                         |                             | RES                         | ERVED-           |                   |                   |                   |                    |

| 0D                 |                  |                         |                             | RES                         | ERVED-           |                   |                   |                   |                    |

| 0E                 | PD               | Tfhp                    | DialEn                      | -                           | -                | B2/B1             | RxMute            | TxMute            | Control Register 1 |

| 0F                 | RST              | -                       | A/µ                         | Smag/<br>CCITT              | RxINC            | TxINC             | -                 | -                 | Control Register 2 |

| 10                 | -                | ST <u>-BU</u> S/<br>SSI | CEN                         | DEN                         | D <sub>8</sub>   | Asynch/<br>Synch  | CSL1              | CSL <sub>0</sub>  | FDI Control        |

| 11                 | -                | -                       | -                           | $W_4$                       | $W_3$            | W <sub>2</sub>    | W <sub>1</sub>    | W <sub>0</sub>    | Watchdog           |

| 12                 | -                | -                       | -                           | -                           | b <sub>3</sub>   | b <sub>2</sub>    | b <sub>1</sub>    | b <sub>0</sub>    | Tx Path Control    |

| 13                 | b <sub>7</sub>   | b <sub>6</sub>          | b <sub>5</sub>              | b <sub>4</sub>              | b <sub>3</sub>   | b <sub>2</sub>    | b <sub>1</sub>    | b <sub>0</sub>    | Rx Path Control    |

| 14                 | b <sub>7</sub>   | b <sub>6</sub>          | b <sub>5</sub>              | b <sub>4</sub>              | b <sub>3</sub>   | b <sub>2</sub>    | b <sub>1</sub>    | b <sub>0</sub>    | C-Channel Register |

| 15                 | D <sub>7</sub>   | D <sub>6</sub>          | $D_5$                       | D <sub>4</sub>              | $D_3$            | D <sub>2</sub>    | D <sub>1</sub>    | D <sub>0</sub>    | D-Channel Register |

| 16                 |                  |                         |                             | RES                         | ERVED-           |                   |                   |                   |                    |

| 17                 | -                | -                       | Loop <sub>2</sub>           | Loop <sub>1</sub>           | -                | -                 | -                 | -                 | Loopback Register  |

| 18                 | HiEN             | LoEn                    | DTMF<br>StEn                | Ring En                     | -                | -                 | -                 | WR                | DTMF/Tone Ringer   |

| 19                 | TxG <sub>3</sub> | TxG <sub>2</sub>        | TxG <sub>1</sub>            | TxG <sub>0</sub>            | $RxG_3$          | RxG <sub>2</sub>  | RxG <sub>1</sub>  | RxG <sub>0</sub>  | Digital Gain       |

| 1A                 | L <sub>7</sub>   | $L_6$                   | $L_5$                       | L <sub>4</sub>              | $L_3$            | L <sub>2</sub>    | L <sub>1</sub>    | L <sub>0</sub>    | Low Tone Coeff     |

| 1B                 | H <sub>7</sub>   | H <sub>6</sub>          | $H_5$                       | H <sub>4</sub>              | H <sub>3</sub>   | H <sub>2</sub>    | H <sub>1</sub>    | H <sub>0</sub>    | High Tone Coeff    |

| 1C                 | Enable           | -                       | MS <sub>1</sub>             | MS <sub>0</sub>             | -                | Pad <sub>2</sub>  | Pad <sub>1</sub>  | Pad <sub>0</sub>  | Anti-Howl Control  |

| 1D                 | -                | TH <sub>h6</sub>        | $\mathrm{TH}_{\mathrm{h5}}$ | $\mathrm{TH}_{\mathrm{h4}}$ | TH <sub>h3</sub> | TH <sub>h2</sub>  | TH <sub>h1</sub>  | TH <sub>h0</sub>  | High Threshold     |

| 1E                 | -                | TH <sub>I6</sub>        | TH <sub>I5</sub>            | TH <sub>I4</sub>            | TH <sub>I3</sub> | TH <sub>I2</sub>  | TH <sub>I1</sub>  | TH <sub>I0</sub>  | Low Threshold      |

| 1F<br>•<br>•<br>3F | RESERVED         |                         |                             |                             |                  |                   |                   |                   |                    |

## **Register Summary**

#### ADDRESSES = 00h to 09h ARE RESERVED

| Filter Co | dec Con                   | trol Reg          | ister 1               |                   |             |                   |                          | ADDRI             | ESS = 0Ał | า WRITE/R         | EAD VERIFY         |

|-----------|---------------------------|-------------------|-----------------------|-------------------|-------------|-------------------|--------------------------|-------------------|-----------|-------------------|--------------------|

|           | -                         | RxFG <sub>2</sub> | RxFG <sub>1</sub>     | RxFG <sub>0</sub> | -           | TxFG <sub>2</sub> | TxFG <sub>1</sub>        | TxFG <sub>0</sub> |           |                   | eset Value<br>X000 |

|           | 7                         | 6                 | 5                     | 4                 | 3           | 2                 | 1                        | 0                 |           |                   |                    |

|           |                           |                   |                       |                   |             | 1 [               |                          |                   |           |                   | 1                  |

|           | ceive Gain<br>etting (dB) | Rx                | FG <sub>2</sub>       | RxFG <sub>1</sub> | $RxFG_0$    | -                 | Fransmit G<br>Setting (d |                   | $TxFG_2$  | TxFG <sub>1</sub> | TxFG <sub>0</sub>  |

| (         | (default) 0               |                   | 0                     | 0                 | 0           |                   | (default)                | 0                 | 0         | 0                 | 0                  |

|           | -1                        |                   | 0                     | 0                 | 1           |                   | 1                        |                   | 0         | 0                 | 1                  |

|           | -2                        |                   | 0                     | 1                 | 0           |                   | 2                        |                   | 0         | 1                 | 0                  |

|           | -3                        |                   | 0                     | 1                 | 1           |                   | 3                        |                   | 0         | 1                 | 1                  |

|           | -4                        |                   | 1                     | 0                 | 0           |                   | 4                        |                   | 1         | 0                 | 0                  |

|           | -5                        |                   | 1                     | 0                 | 1           |                   | 5                        |                   | 1         | 0                 | 1                  |

|           | -6                        |                   | 1                     | 1                 | 0           |                   | 6                        |                   | 1         | 1                 | 0                  |

|           | -7                        |                   | 1                     | 1                 | 1           |                   | 7                        |                   | 1         | 1                 | 1                  |

|           |                           |                   | RxFG <sub>n</sub> = I | Receive Fi        | lter Gain n |                   |                          |                   | TxFG      | n = Transmit      | Filter Gain n      |

|           | Gain3      | Gain2 | Gain1 | Gain0    | -     | STG <sub>2</sub> | STG <sub>1</sub> | STG <sub>0</sub> |                  | Power Res<br>0010 2     |                  |

|-----------|------------|-------|-------|----------|-------|------------------|------------------|------------------|------------------|-------------------------|------------------|

| L         | 7          | 6     | 5     | 4        | 3     | 2                | 1                | 0                |                  |                         |                  |

| Speake    | r Gain (dl | B)    |       | <b>0</b> |       |                  | Side-tone        | e Gain           |                  |                         |                  |

| Gain3 = 1 | Gain       | 3 = 0 | Gain2 | Gain1    | Gain0 |                  | Setting          | (dB)             | STG <sub>2</sub> | STG <sub>1</sub>        | STG <sub>0</sub> |

| 16        | 8          |       | 0     | 0        | 0     |                  | (default)        | OFF              | 0                | 0                       | 0                |

| 12        | 4          |       | 0     | 0        | 1     |                  | 9.9              |                  | 0                | 0                       | 1                |

| 8         | 0          |       | 0     | 1        | 0     |                  | -6.6             | 4                | 0                | 1                       | 0                |

| 4         | -4         | 1     | 0     | 1        | 1     |                  | -3.3             | 2                | 0                | 1                       | 1                |

| 0         | -8         | 3     | 1     | 0        | 0     |                  | 0                |                  | 1                | 0                       | 0                |

| -4        | -1         | 2     | 1     | 0        | 1     |                  | 3.32             | 2                | 1                | 0                       | 1                |

| -8        | -1         | 6     | 1     | 1        | 0     |                  | 6.64             | 1                | 1                | 1                       | 0                |

| -12       | -2         | 0     | 1     | 1        | 1     |                  | 9.96             | 6                | 1                | 1                       | 1                |

|           |            |       |       |          |       |                  |                  |                  |                  | STG <sub>n</sub> = Side |                  |

ADDRESS = 0Ch RESERVED

#### ADDRESS = 0Dh RESERVED

| Control R | egister        | 1          |                              |             |              |             |            | ADDRI        | ESS = 0Eh WRITE/READ VERIF                                                          |

|-----------|----------------|------------|------------------------------|-------------|--------------|-------------|------------|--------------|-------------------------------------------------------------------------------------|

|           | PD             | Tfhp       | DialEN                       | -           | -            | B2/B1       | RxMute     | TxMute       | Power Reset Value<br>100X X000                                                      |

|           | 7              | 6          | 5                            | 4           | 3            | 2           | 1          | 0            |                                                                                     |

| PD        | When           | high, the  | crystal osc                  | illator and | FDI blocks   | s are powe  | ered down. | When low     | , the oscillator and FDI circuits are active                                        |

| Tfhp      |                | 0          | additional<br>ss filter is c | •••         | function (p  | assband     | beginning  | at 400 Hz)   | ) is inserted into the transmit path. Wher                                          |

| DialEN    | When<br>disabl | 0          | rst order lov                | wpass filte | r is inserte | ed into the | receive pa | ath (3 dB =  | 1.2 kHz). When low, this lowpass filter is                                          |

| B2/B1     |                | •          |                              |             | •            |             |            |              | w, the receive Filter/CODEC operates or<br>nd is ignored for SSI operation.         |

| RxMUTE    |                | 0          | received P<br>en low the     |             |              | •           | •          | with quiet o | code; thus forcing the receive path into a                                          |

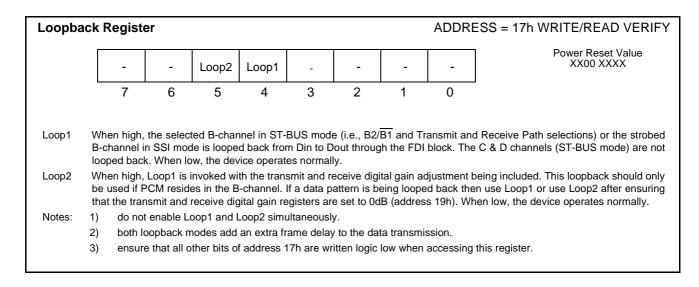

| TxMUTE    | mute           | state (onl |                              | ut code is  | muted, th    | ie transmi  | •          | •            | code; thus forcing the output code into a ansmit Filter/CODEC are still functional) |